# Influence of halo and source/drain implant variations on the drive current in p-channel vertical double gate MOSFET

K.E. Kaharudin<sup>1,2,\*</sup>, F. Salehuddin<sup>1,2</sup>, A.S.M. Zain<sup>1,2</sup>, M.N.I.A. Aziz<sup>1,2</sup>

<sup>1)</sup> Faculty of Electronics and Computer Engineering, Universiti Teknikal Malaysia Melaka, Hang Tuah Jaya, 76100 Durian Tunggal, Melaka, Malaysia

<sup>2)</sup> Centre for Telecommunication Research and Innovation, Universiti Teknikal Malaysia Melaka, Hang Tuah Jaya, 76100 Durian Tunggal, Melaka, Malaysia

\*Corresponding e-mail: khairilezwan@yahoo.com.my

Keywords: ANOVA; drive current; Taguchi

**ABSTRACT** – This paper describes an investigation on the influence of process parameters such as Halo and Source/Drain (S/D) implantation on drive current (I<sub>ON</sub>) in p-channel vertical DG-MOSFET device was done by utilizing L<sub>9</sub> orthogonal array Taguchi method. The level of significance for each process parameters on I<sub>ON</sub> were determined by using analysis of variance (ANOVA). The virtual fabrication and electrical characterization of the device were performed by using a process simulator (ATHENA) and a device simulator (ATLAS) respectively. This procedure was followed by Taguchi modeling to aid in optimizing the process parameters variation towards I<sub>ON</sub>. Based on the final results, the most dominant factor that affecting I<sub>ON</sub> value was found to be S/D implant energy with 99% of factor effects on signal-to-noise ratio (SNR). Meanwhile, the highest possible  $I_{ON}$  value was found to be 323.2 mA/ $\mu$ m.

#### 1. INTRODUCTION

Over the past decades, a physical gate length (Lg) of MOSFET devices has been attempted to be reduced while keeping good electrical performance. For achieving a physical gate length (Lg) lower than 22nm with excellent device characteristics, a very careful design of channel doping profiles is required. Halo or pocket and source/drain implantation is widely utilized in deep submicron MOSFET technologies. These implant can be independently adjusted to prevent puchthrough effect. The dopant spread in the channel region can be suppressed by to reduce the body effect.

Optimization of the process parameters is a key step in the Taguchi method in order to achieve better device characteristics. The Taguchi method involves an analysis that is capable of identifying the most significant factors in achieving the higher I<sub>ON</sub> value in which the level of these factors should be adjusted in term of their dosage and energy [1]. The optimization of process parameters using Taguchi method is insensitive to the variation of environmental conditions and noise factors [2]. Basically, the traditional process parameter design developed by Fisher [3], is very complex, especially when involving a large number of experiments. However, Taguchi method utilizes a special design of orthogonal arrays to analyze the entire process parameters space by using a small number of experiments. Besides that, Taguchi method utilizes a

signal-to-noise ratio (SNR) analysis to analyze the experimental data that could help in figuring out the optimal parametric combination [4].

In this work, an analytical model of two-dimensional p-channel Vertical DG-MOSFET device is developed by using Silvaco Technology Computer Aided Design (TCAD) simulation software, where the effects of halo and source/drain implant variation are investigated using Taguchi method. The Taguchi method is also utilized to reveal the ideal level of dosage and energy of halo and source/drain (S/D) implantation for the higher  $I_{\rm ON}$  value of Vertical DG-MOSFET device.

#### 2. MATERIALS AND METHODS

# 2.1 Process simulation

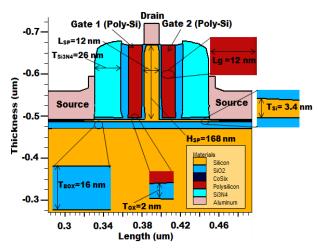

The completed structure of p-channel Vertical DG-MOSFET device is illustrated as in Figure 1.

Figure 1 Structure of p-channel vertical DG-MOSFET.

# 3. RESULTS AND DISCUSSION

#### 3.1 Characterization of p-channel vertical DG-MOSFET

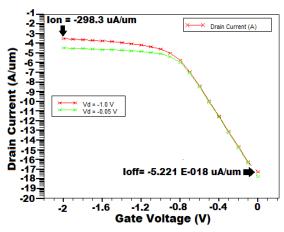

Figure 2 shows the graph of subthreshold drain current ( $I_D$ ) versus gate voltage ( $V_G$ ) at drain voltage  $V_D$  = - 0.05 V and  $V_D$  = - 1.0 V for p-channel Vertical DG-MOSFET device. The value of off-leakage current ( $I_{OFF}$ ) and drive current ( $I_{ON}$ ) were extracted from the graph.

Figure 2 Graph of subthreshold drain current (I<sub>D</sub>) versus gate voltage (V<sub>G</sub>).

# 3.2 Signal-to-Noise ratio (SNR) analysis

The type of signal-to-noise (SNR) analysis that was assigned to analyze the  $I_{ON}$  values was higher-the-better. The SNR (higher-the-better),  $\eta$  can be expressed as [5]:

$$\eta = -10Log_{10} \left[ \frac{1}{n} \sum_{i=1}^{n} \frac{1}{y^2} \right]$$

(1)

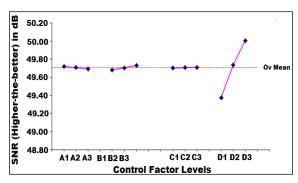

The factor effects graph for SNR (Higher-thebetter) was plotted as illustrated in Figure 3. The dashed horizontal lines in both graphs represent the overall mean of SNR (Higher-the-better) which is 49.71dB.

Figure 3 Factor effects graph for SNR (Higher-the-better).

# 3.3 Analysis of Variance (ANOVA)

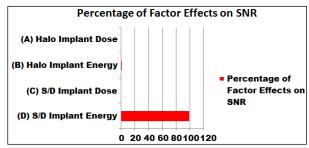

The percent factor effect on SNR indicates the priority of a factor (process parameter) to reduce variation. For a factor with a high percentage of contribution and a small variance (mean square) will have a great influence on the device's performance. The percentages of factor effect on SNR of all factors are visualized in Figure 4.

# 4. CONFIRMATION TEST

The final step is to verify the improvement of the device's characteristic by simulating the device using the best setting of process parameters. The results of the final simulation of the device are shown in Table 1.

Figure 4 Pareto plot of factor effects on SNR for I<sub>ON</sub>.

Table 1 Final result of confirmation test for drive current.

|   | Drive Current, I <sub>ON</sub> (mA/µm) |                  |                  |            | SNR          |

|---|----------------------------------------|------------------|------------------|------------|--------------|

|   | I <sub>ON1</sub>                       | I <sub>ON2</sub> | I <sub>ON3</sub> | $I_{ON4}$  | (Higher-the- |

|   | $(U_1V_1)$                             | $(U_1V_2)$       | $(U_2V_1)$       | $(U_2V_2)$ | best)        |

| , | 323.2                                  | 318.8            | 318.3            | 312.2      | 50.01 dB     |

#### 5. CONCLUSIONS

As conclusions, the optimum solution in obtaining the highest possible value of drive current (I<sub>ON</sub>) value was successfully predicted by L9 orthogonal array Taguchi method. Drive current (I<sub>ON</sub>) is the main response that has been investigated in this project as it is regarded as the main factor to decide the functionality of p-channel Vertical DG-MOSFET device. The level of significance of process parameters on I<sub>ON</sub> is determined by using analysis of variance (ANOVA). Based on ANOVA method, the process parameter that has the major influence on I<sub>ON</sub> was identified to be S/D implant energy with a percentage of 99% (factor effects on SNR). The highest possible drive current (I<sub>ON</sub>) value was observed to be 323.2 mA/µm by using the optimized combination level of halo and S/D implantation predicted by Taguchi method.

#### REFERENCES

- [1] F. Salehuddin, I. Ahmad, F. A. Hamid, A. Zaharim, H. A. Elgomati, B. Y. Majlis, P. R. Apte, "Influence of HALO and Source / Drain Implantation Variations on Threshold Voltage in 45nm CMOS Technology," *International Journal of Electronics Communication and Computer Technology*, Vol. 2, no. 3, pp. 27-33, 2012.

- [2] K. Yang, E. C. Teo, F. Fuss, "Application of Taguchi Method in Optimization of Cervical Ring Cage," *International Journal of Biomechanics*, Vol. 40, no. 14, pp. 3251-3256, 2007.

- [3] M. Nalbant, H. Gokkaya, G. Sur, "Application of Taguchi method in the optimization of cutting parameters for surface roughness turning," *International Journal Design*, Vol. 28, pp. 1379-1385, 2007.

- [4] U. Esme, "Application of Taguchi Method for the Optimization of Resistance Spot Welding Process," *Arabian Journal for Science and Engineering*, Vol. 34, pp. 519-528.

- [5] M. S. Phadke, *Quality Engineering Using Robust Design*, Pearson Education, Inc. and Dorling Kindersley Publishing, Inc; 2001.